# **Crnch Rogues Gallery Documentation**

Release 1.0

**Crnch Rogues Gallery**

# **GENERAL TOPICS**

| 1  | What is the Rogues Gallery?         | 3  |

|----|-------------------------------------|----|

| 2  | Getting Started with Rogues Gallery | 5  |

| 3  | Rogues Gallery Hardware             | 9  |

| 4  | Rogues Gallery Filesystems          | 13 |

| 5  | Mailing Lists and Requesting Help   | 15 |

| 6  | Vendor Forums                       | 19 |

| 7  | Contributing to this Documentation  | 21 |

| 8  | Testbed Release Notes               | 25 |

| 9  | RG Documentation Authors            | 27 |

| 10 | Using Slurm with RG Systems         | 29 |

| 11 | Open OnDemand                       | 33 |

| 12 | Visual Studio Code                  | 43 |

| 13 | Python Environments                 | 47 |

| 14 | Jupyter Notebooks                   | 55 |

| 15 | Using Scrontab with Slurm           | 59 |

| 16 | Using GUI Applications with VNC     | 61 |

| 17 | CI/CD Support                       | 69 |

| 18 | Rogues Gallery Workflows            | 71 |

| 19 | Profilers                           | 75 |

| 20 | Instinct - AMD MI210                | 77 |

| 21 | Quorra - NVIDIA Ampere GPUs         | 81 |

| 22 | Violet - Sapphire Rapids            | 83 |

|    |                                     |    |

| 23        | Octavius - A64FX Testbed                     | 85  |

|-----------|----------------------------------------------|-----|

| 24        | Kingpin - NVIDIA DevKit Systems              | 91  |

| 25        | Lucata Pathfinder Getting Started            | 93  |

| 26        | Lucata Pathfinder FAQs                       | 97  |

| 27        | Rudi2 - Jetson AGX Orin                      | 99  |

| 28        | Smart Networking - Getting Started           | 101 |

| 29        | Bluefield-2 DPU                              | 103 |

| 30        | cuQuantum                                    | 105 |

| 31        | Xilinx FPGAs - Getting Started               | 107 |

| 32        | Xilinx Vivado Flow                           | 111 |

| 33        | PYNQ cluster                                 | 113 |

| 34        | Xilinx Smart SSD                             | 115 |

| 35        | Vortex RISC-V GPGPU                          | 117 |

| 36        | Xilinx ML Tools                              | 119 |

| 37        | Intel OneAPI for Reconfigurable Computing    | 123 |

| 38        | Using Intel OneAPI with CRNCH Rogues Gallery | 127 |

| 39        | FPGA Power Measurement                       | 133 |

| 40        | RISC-V Hardware                              | 137 |

| 41        | Frozone                                      | 139 |

| 42        | Power Monitoring                             | 141 |

| 43        | CRNCH Rogues Gallery Tutorials               | 143 |

| 44        | Near-memory Resources                        | 145 |

| 45        | GraphBLAS Resources                          | 147 |

| 46        | Neuromorphic Computing Resources             | 151 |

| <b>47</b> | Quantum Computing Resources                  | 155 |

| 48        | Related Testhed Resources                    | 159 |

The Rogues Gallery is a new concept focused on developing our understanding of next-generation hardware with a focus on unorthodox and uncommon technologies. This project, initiated by Georgia Tech's Center for Research into Novel Computing Hierarchies (CRNCH), will acquire new and unique hardware (ie, the aforementioned "rogues") from vendors, research labs, and startups and make this hardware available to students, faculty, and industry collaborators within a managed data center environment. By exposing students and researchers to this set of unique hardware, we hope to foster cross-cutting discussions about hardware designs that will drive future performance improvements in computing long after the Moore's Law era of "cheap transistors" ends.

To see what hardware the Rogues Gallery currently includes, please see our hosted hardware page. For more information on the initial Rogues Gallery vision, please see our recent presentation at the 2021 CRNCH Summit [Slides] [Talk].

For updated status on the testbed please see our Spring 2022 talk [Slides]

**NSF Acknowledgment**: The Rogues Gallery testbed is primarily supported by the National Science Foundation (NSF) under NSF Award Number #2016701. Any opinions, findings and conclusions, or recommendations expressed in this documentation are those of the author(s), and do not necessarily reflect those of the NSF.

GENERAL TOPICS 1

2 GENERAL TOPICS

#### WHAT IS THE ROGUES GALLERY?

The Rogues Gallery is a shared, open-access testbed run by the Center for Research into Novel Computing Hierarchies (CRNCH) at Georgia Tech. This testbed is focused on supporting "post-Moore" architectures, tools, and software. The RG testbed is currently funded by NSF's Community CISE Research Infrastructure (CCRI) program as NSF award #2016701 starting in September 2020. The Rogues Gallery was started as a Georgia Tech specific testbed in 2017, and it has since grown to close to over 100 internal and external users.

# 1.1 What is in the Rogues Gallery?

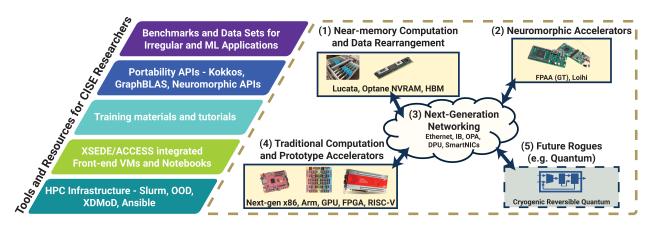

Currently the Rogues Gallery has support for devices in the near-memory, traditional HPC, reconfigurable, and neuro-morphic spaces. The CCRI grant will enable us to expand that to networking and quantum-related testbed equipment. The figure below shows a high-level overview of what the Rogues Gallery testbed looks like.

This testbed is meant to enable several CISE-specific research pillars including: 1) sparse and irregular HPC 2) hardware and software codesign 3) novel machine learning systems 4) and edge computing and next-generation networking.

#### **CISE Enabled Research Pillars**

#### Sparse/Irregular HPC

- Graph analytics

- Scientific Computing

- Database and Big Data Acceleration

#### HW/SW Codesign

- Polyhedral compilation,

- Design of libraries, runtimes, APIs for novel devices

- Benchmarking and characterization

#### Machine Learning

- Low-power edge Al

- Autonomous vehicles

- SLAM for robotics

- Dynamic and life-long learning

#### Next-generation Networking

- 5G software stacks

- Edge computing services

- In-situ and encrypted data analysis

- Data reduction and linespeed DSP

#### Rogues Gallery Hardware and Software Support

- Emu Pathfinder

- FPGA+HBM

- CASPIAN

- Tensor, Streaming Graph APIs

- ARM A64FX

- Emu Pathfinder

- FPGAs + RISC-V

- Optane

- Kokkos, Habanero-C runtimes

- FPAA and CASPIAN

- EMU Pathfinder

- FPGAs

- RASP/TENNLabSW

- Emu Scikit-learn

- Ettus USRP-2947 and Ettus E-320

- Mellanox Bluefield NICs

- FPGAs

- FPAA and CASPIAN

#### 1.2 Who are the users?

Anyone in the US can request an account for the CRNCH Rogues Gallery testbed with priority for CISE researchers, students, and industry partners.

# 1.3 How do I acknowledge the use of Rogues Gallery resources?

Please see our project page on citing the usage of the Rogues Gallery. This helps us acknowledge NSF and other support and assists in the growth of the testbed!

**CHAPTER**

**TWO**

#### GETTING STARTED WITH ROGUES GALLERY

# 2.1 How do I request an account on the Rogues Gallery (RG)?

Users should request a new account using our form on the CRNCH page here. Note that it may take 2-3 business days for your account to be added after you are approved.

For both internal and external users, we ask for "an RG contact". If you've talked to one of the key personnel for the RG testbed you can put this person down, or you can put down your research advisor if you are external to GT but working at a university.

For GT users, please put your research advisor or down one of the testbed personnel you have talked to. We will also need your GT (Passport) username to add login access for you.

**NOTE:** For GT faculty or staff looking to add new *external* users, it is very helpful to us if you can sponsor the users as Passport guests. Then the above form can be filled out with the external user's guest username which helps to streamline the access process. You can sponsor a guest account with Passport for up to one year and then renew the user if they are still an active collaborator.

#### 2.2 How do I Access RG machines?

NOTE: You should use your GT Passport username (e.g, gburdell3) and password to access all CRNCH RG nodes and resources!

Once you receive a note that your account has been approved, you can test your login to the testbed. To access Rogues Gallery machines from off campus you need to either

1) SSH to the testbed via the login node from a terminal session.

OR

2) Use Open OnDemand for a GUI-based session. See this page for more information on using Open OnDemand

For SSH, you should use your Georgia Tech account username and password to log into all nodes using the gateway login node, rg-login.crnch.gatech.edu. rg-login is available from off the campus network and the VPN, and other nodes are accessible from the login node. As an example:

$< your machine > \$ \ ssh \ < your-gt-acctname > @rg-login.crnch.gatech.edu \\ rg-login.crnch.gatech.edu$

This is the main RG login node. From this node you can access all CRNCH resources. To ⇒see a complete list of available hardware please visit: https://gt-crnch-rg.

(continues on next page)

(continued from previous page)

→readthedocs.io/en/main/general/rg-hardware.html

<your-gt-acctname>@#rg-login\$

Once you've logged in, you can use Slurm to request other nodes within the testbed. See more information on Slurm at this page.

Note that you can also use VSCode to log into the Rogues Gallery via its terminal functionality. See this page for more details.

# 2.3 What machines are available in the Rogues Gallery?

Note that all machines have a .crnch.gatech.edu suffix and some examples include:

- rg-login login VM for off-campus access. Used as a gateway node

- rg-emu-dev: VM for Emu compilation and simulation

- rg-fpga-dev-<1-4>: VMs for FPGA compilation and simulation

- rg-neuro-dev: VM for neuromorphic tools

- Please see this page for a complete list of available machines in the RG testbed

# 2.4 VPN Requirements (for GT users only)

You can access all CRNCH resources using login nodes like *rg-login* or the Open OnDemand web interface. However, you can also use GT's VPN solution as an alternative to access some VMs and nodes directly. Note that this may require that you set up two-factor authentication on your phone and link it with your account name. You shouldn't need to use the VPN to access Rogues Gallery resources and materials, but for special requirements please email us at *crnch-rg-help@cc.gatech.edu*.

Other Georgia Tech resources like PACE's Phoenix cluster require the usage of the VPN, and you can read more about these requirements at their site

#### 2.5 How do I work with novel architecture of interest X?

First of all, check the sidebar for the appropriate architecture category and read through the existing documentation. Note that we are migrating some of our pages from our internal wiki to this public ReadTheDocs site over the next few months. You can use your GT username and password to log into the internal wiki.

Once you have done this, if you have questions please ask on Teams or via help ticket.

- Rogues Gallery Hardware Master List

- Lucata Pathfinder Getting Started

- · Reconfigurable Computing HW and Tools

- Intel FPGAs Getting Started

- Xilinx FPGAs Getting Started

- Quantum Computing

- Neuromorphic Computing

- Smart Networking

- RISC-V

# 2.6 What are some best practices for using the RG hardware?

- 1. Make sure to back your code up, preferably with a GT Github or external Github repository. While we do have a shared filesystem, this can possibly experience a hardware failure.

- 2. Use tmux or screen on the login and development VMs, especially when running tests.

# 2.7 How do I ask for assistance? Is there a mailing list?

Please refer to this page for more details on asking for help and posting to RG community groups and mailing lists.

| <b>Crnch Rogues Gallery Documentation, Release 1.0</b> | ) |

|--------------------------------------------------------|---|

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

|                                                        |   |

#### ROGUES GALLERY HARDWARE

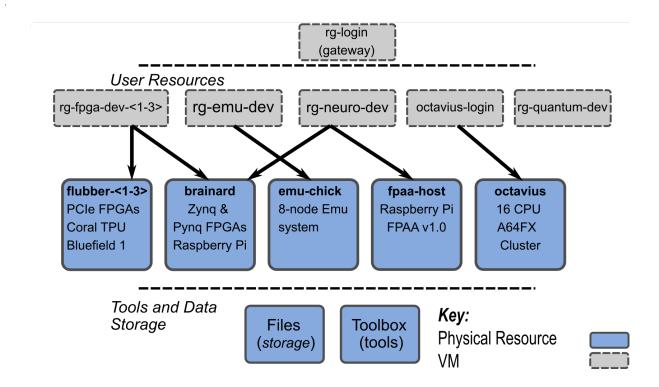

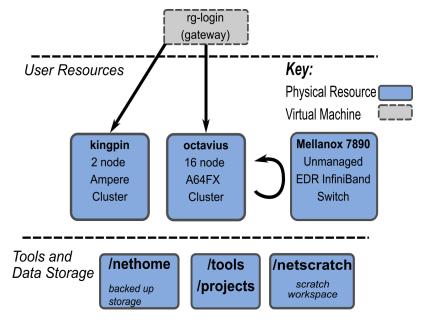

The Rogues Gallery testbed is composed of both "virtual" resources and "physical" servers and test platforms. The figure below shows the Rogues Gallery resources at a high level with suggested paths from development VMs to the actual hardware. Discussion of the filesystems you have access to can be found here.

For instance, if you're able to test your compilation and do debugging on the rg-fpga-dev VMs, you can then use the same code on the physical "flubber" boxes to test your code with a PCI Express-based FPGA. We currently have three pairs of development VMs that map to physical hardware, as described more in the tables below.

#### 3.1 RG Virtual Machines

Note that VMs are meant as development resources since we may need to reboot physical hardware often to apply new drivers or reconfigure for specific experiments. These VMs have limited CPU cores and memory, but we can reconfigure them as needed or provide additional resources for long-running simulations. Local storage refers to space hosted within the VM for /localscratch. Except where noted, all machines are running RHEL8 or Ubuntu 20.04.

#### 3.1.1 RG Virtual Machines

| Resource             | CPU                    | Memory<br>(GB) | Local<br>(GB) | Storage | Software and Features          |

|----------------------|------------------------|----------------|---------------|---------|--------------------------------|

| rg-emu-dev           | 4 core, E312xx         | 4              | 33            |         | Emu simulator and tools        |

| rg-fpga-dev<1-<br>3> | 4 core, E312xx         | 16             | 250           |         | RHEL 8 VM for FPGA tools       |

| rg-fpga-dev4         | 4 core, E312xx         | 16             | 250           |         | Ubuntu 20.04 VM for FPGA tools |

| rg-neuro-dev         | 4 core, Broad-<br>well | 8              | 450           |         | ROS, FPAA tools                |

| rg-quantum-dev       | 4 core, Broad-<br>well | 8              | 130           |         | XACC, Qiskit                   |

# 3.2 RG Physical Machines

#### 3.2.1 Arm HPC

| Resource       | CPU   | Memory (GB) | Network | Cards | Notes |

|----------------|-------|-------------|---------|-------|-------|

| octavius<1-16> | A64FX | 32 GB HBM2e | EDR IB  |       |       |

#### 3.2.2 Near-Memory

The Pathfinder system consists of 4 chassis while the Emu Chick is a one chassis system. We recommend that you use the newer Pathfinder system for your work.

| Resource                          | Nodes | Memory<br>(GB) | LCEs | Network            | Notes                |

|-----------------------------------|-------|----------------|------|--------------------|----------------------|

| pathfinder (4 chassis)            | 32    | 2048           | 784  | RapidIO 2.0, 10 GE |                      |

| karrawingi (Emu Chick, 1 chassis) | 8     | 512            | 64   | RapidIO, 1 GE      | karrawingi-<br>login |

# 3.2.3 Neuromorphic/Al

| Re-<br>source        | CPU                      | Memory (GB)                        | Network                   | Cards              | Notes                                 |

|----------------------|--------------------------|------------------------------------|---------------------------|--------------------|---------------------------------------|

| quorra1              | 2x AMD EPYC 7502 (Rome)  | 256 DDR4, 3200 MHz,<br>16 GB DIMMs | Bluefield-2<br>NIC, 10 GE | 4x A30             |                                       |

| quorra2              | 2x AMD EPYC 7502 (Rome)  | 256 DDR4, 3200 MHz,<br>16 GB DIMMs | Bluefield-2<br>NIC, 10 GE | 4x A30,<br>1x A100 |                                       |

| rg-<br>fpaa-<br>host | Raspberry Pi<br>Model 3B | 2 GB                               |                           |                    | Hosts FPAA via USB<br>UART connection |

| rudi1                |                          |                                    |                           |                    | Jetson Xavier NX Developer Kit        |

# 3.2.4 Reconfigurable and Novel Networking

| Re-<br>sourc   | CPU                            | Memory (GB)                           | Network                                                                               | Cards                                                   | Notes                         |

|----------------|--------------------------------|---------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|

| flub-<br>ber1  | 2x Intel E5-<br>2630           | 256 DDR4,<br>2133 MHz, 32<br>GB DIMMs | 10 GE                                                                                 | 2x Alveo U50, Coral TPU                                 | NA                            |

| flub-<br>ber2  | 2x Intel Gold 6226R            | 384 DDR4,<br>2666 MHz, 32<br>GB DIMMs | 10 GE                                                                                 | Arria 10 PAC,<br>Bittware 520N                          | NA                            |

| flub-<br>ber3  | 2x Intel Gold 6226R            | 384 DDR4,<br>2666 MHz, 32<br>GB DIMMs | 10 GE, EDR IB                                                                         | Stratix 10 PAC,<br>Bittware 520MX,<br>Bittware 385A-SoC | NA                            |

| flub-<br>ber4  | 2x AMD<br>EPYC 7513<br>(Milan) | 256 DDR4,<br>3200 MHz, 16<br>GB DIMMs | NVIDIA ConnectX-6                                                                     | NA                                                      | NA                            |

| flub-<br>ber5  | 2x AMD<br>EPYC 7513<br>(Milan) | 256 DDR4,<br>3200 MHz, 16<br>GB DIMMs | NVIDIA ConnectX-6                                                                     | Xilinx Alveo U280                                       | NA                            |

| flub-<br>ber6  | 2x AMD<br>EPYC 7513<br>(Milan) | 256 DDR4,<br>3200 MHz, 16<br>GB DIMMs | NVIDIA ConnectX-6, Innova-2<br>Flex, Bluefield-1 NIC, Bluefield-2<br>NIC, Intel N6000 | NA                                                      | Smart<br>Network-<br>ing Node |

| flub-<br>ber7  | 2x AMD<br>EPYC 7513<br>(Milan) | 256 DDR4,<br>3200 MHz, 16<br>GB DIMMs | NVIDIA ConnectX-6, Innova-2<br>Flex, Bluefield-1 NIC, Bluefield-2<br>NIC, Intel N6000 | NA                                                      | Smart<br>Network-<br>ing Node |

| flub-<br>ber8  | 2x Intel<br>Gold 6338          | 512 DDR4,<br>3200 MHz, 32<br>GB DIMMs | NVIDIA ConnectX-6                                                                     | NA                                                      | NA                            |

| flub-<br>ber9  | 2x Intel<br>Gold 6338          | 512 DDR4,<br>3200 MHz, 32<br>GB DIMMs | NVIDIA ConnectX-6                                                                     | NA                                                      | NA                            |

| flub-<br>ber10 | 2x Intel<br>Gold 6338          | 512 DDR4,<br>3200 MHz, 32<br>GB DIMMs | NVIDIA ConnectX-6                                                                     | NA                                                      | NA                            |

#### 3.2.5 Devboard Hosts

| Re-<br>source | CPU           | Memory (GB)                          | Net-<br>work | Cards Notes                                           |

|---------------|---------------|--------------------------------------|--------------|-------------------------------------------------------|

| brainard      | i5-<br>10210U | 32 GB DDR4, 2666 MHz, 16<br>GB DIMMs | 1 GE         | Connection to RISC-V board and FPGA, Intel NUC10i5FNK |

# 3.2.6 RISC-V

| Resource         | CPU                                | Memory<br>(GB) | Net-<br>work | Notes                         |

|------------------|------------------------------------|----------------|--------------|-------------------------------|

| johnny-rv5-<br>1 | 4xU74 cores and 1xS7 core, 1.4 GHz | 16 GB DDR4     | 1 GE         | SiFive Unmatched mother-board |

# 3.2.7 Simulation and Tutorial Machines

| Resource             | CPU              | Memory (GB) | Network | Notes                      |

|----------------------|------------------|-------------|---------|----------------------------|

| hawksbill / notebook | 4x Intel E7-4820 | 1024 DDR3   | 1 GE    | Used for Jupyter notebooks |

# 3.3 Techfee Systems

| Re-<br>source   | CPU                  | Memory (GB)                       | Network                         | Cards                  | Notes                          |

|-----------------|----------------------|-----------------------------------|---------------------------------|------------------------|--------------------------------|

| frozone<1<br>4> | 2x Ice Lake<br>8352Y | 256 DDR4, 3200GHz,<br>16 GB DIMMs | Omni-Path 100 GB,<br>100HFA16LS | 1.6TB<br>P5800X<br>SSD | FY 2021 TechFee<br>Acquisition |

#### ROGUES GALLERY FILESYSTEMS

*Note*: We strongly encourage you to do compilation (especially for FPGAs) using /netscratch and back up your project files to the backed up "nethome" or /home/<username directory. Code should additionally be backed up to a Github repo - remember the policy of keeping two separate copies of all important code/data!

#### 4.1 Quotas and Data Retention Policies

#### **4.1.1 Quotas**

We have the following quotas for users, subject to future modifications:

- /home 50 GB is provided to each user and is backed up using ZFS snapshots and RAID.

- /project Quotas vary but are typically in the 200 GB range depending on how many users are using a shared project.

- /netscratch no quota limits but please note the lack of backups and data retention policies below. You can find a symlink to netscratch at <user\_home>/USERSCRATCH

#### 4.1.2 Data retention policies

- Backups are provided via a standard fileserver with RAID and ZFS snapshot backups. *However*, we do not guarantee data backups and we recommend you use Github or GT Github for code backups and GT's Box service or PACE-provided storage for large data backups.

- Deactivated accounts will have their data kept for 180 days (~6 months) and it will then be archived and removed at the discretion of the testbed maintainers.

- Scratch data will be *purged* after 120 days without user modification from both /localscratch and / netscratch. Note that scratch explicitly is not backed up, and we cannot restore deleted files.

# 4.2 Storage on CRNCH Systems

#### 4.2.1 Shared home

Each user has **50 GB** of shared storage space mounted under /nethome/<user> that is backed up via our data server (RAID 10) and that is served up via NFS. This storage is relatively stable and is meant for users to keep files consistent across Rogues Gallery resources. **NOTE:** We still strongly encourage users to back up their code using a git repo, such as those provided for free via Georgia Tech's github.gatech.edu.

#### 4.2.2 Shared tools

The Rogues Gallery VMs and physical resources are served by a shared /tools/ directory that contains common tools for each architecture and that is shared via NFS to all available login, development, and experimental nodes.

#### 4.2.3 Shared project space

Individual users may also request joint project space by emailing the admins at crnch-rg-help@cc.gatech.edu. These are served under /projects/ and include space for data sets /projects/bigdata and other lab-based project groups.

#### 4.2.4 Net scratch space

Speedforce.crnch.gatech.edu provides 47 TB of RAID 5 NVMe-backed storage that is mounted at /netscratch on each VM and CRNCH node. Please create a directory for your username and keep your data within this file. Note the data retention policies listed above that is enforced by modification time and cron job scripts. Any unmodified data older than **120 days** is subject to deletion, and users with very large data requirements may be asked to help purchase project-specific storage.

#### 4.2.5 Local scratch space

Note that physical resources like flubber typically have their own fast scratch space, usually mounted at / localscratch. These are local scratch storage locations that are **not backed up** and are meant for temporary output that is then placed under a project or nethome folder. VMs also typically will have a /localscratch that is just using extra HD space in the VM that is a bit faster than the backed up /nethome but that is slower than /netscratch.

We recommend that you use /netscratch instead of local scratch as this is shared across all machines. Both types of scratch have the same data retention policies.

#### MAILING LISTS AND REQUESTING HELP

# 5.1 Help and Mailing List FAQs

- Request access to the MS Teams group. If you are external to GT, please send us a ticket to add you.

- We also have a CRNCH RG Slack workspace here if you have trouble connecting to Teams. Most of the

Lucata discussion currently uses this Slack. Just note that since we are on a free plan that old conversations

are not saved.

- How to use the help ticket webform at https://crnch-rg.cc.gatech.edu/crnch-rg-help/

- The main CRNCH help ticket email address is crnch-rg-help@cc.gatech.edu. We would prefer if you use the webform but the email address is ok if you include your GT username (e.g., gburdell3 for George Burdell).

# 5.2 Help for the CRNCH Rogues Gallery

The Rogues Gallery testbed is rapidly growing along with its support structures. In general, we try to respond to help tickets within 1 business day of your request. Note that the admins and researchers for this project work 9-6 ET Monday-Friday, so any requests outside of this timeframe will be delayed at least until the next business day. Tickets submitted over the weekend or on any GT holidays will be evaluated on the following business day. Please note that Georgia Tech is officially closed for the last week of each calendar year for the Christmas holiday.

# 5.3 How do I request help?

The Rogues Gallery uses a Request Tracker (RT) based ticketing system. You can submit tickets ideally via the webform or alternatively using the email address, crnch-rg-help@cc.gatech.edu. We would request that you submit a help ticket for anything that is not a discussion or minor clarification question. This helps us track specific issues for users and also is important as a metric for our funded testbed project.

That said, the general process for asking for help is:

- 1. Check through the appropriate documentation on the public documentation or the internal wiki to see if this answers your question.

- 2. Ask a clarification question in the related MS Teams group. For example, if you are working with Alveo boards you may want to post your question in the fpga-xilinx channel on Teams.

- Alternatively, if you are not able to use Teams you can post your question on the related mailing list. So for Alveo boards, this would be crnch-rg-reconfig@lists.gatech.edu

- 3. During discussion on the Teams or email group we may move your question to the ticketing system or a private conversation if it is specific to your account. When possible, we'd like to keep most discussion in the appropriate channel as it provides a good reference for other users who may have the same issue.

- Submit tickets to the crnch-rg-help@cc.gatech.edu email address or ideally via the webform at https://crnch.gatech.edu/crnch-rg-help

- 4. As you get to more in-depth research, you may need to pose your question to an external vendor since most architectures in RG are very new and GT researchers and staff are constantly learning along with you. More information on specific vendor forums can be found from this link.

# 5.4 How do I ask a good question?

This is not meant to be a put down! Asking your question in a clear and meaningful way is the easiest way to get assistance. We generally recommend the following for asking a clear suggestion:

- 1. Share the machine name you are having issues with: Ex: "Python notebooks don't run on rg-neuro-dev.crnch.gatech.edu"

- 2. If possible, share the output using quotes or an attached log file. Please share output as text where possible instead of a screenshot!. If we are trying to recreate a problem you have it is much easier to copy and paste text than decipher it from a screenshot.

- 3. Create a "minimum working/reproducible example" (MWE/MRE). In many cases, sharing a huge log file for a full application is not useful to you or to the maintainers of a particular system. See this page on creating an effective MWE: MWE overview

- 4. Don't just state "Feature X doesn't work!". We'll ask you more follow-up questions so it's best to share more detail initially to get your question answered in a prompt fashion.

# 5.5 Rogues Gallery Mailing Lists and Teams Group

There are mailing lists for general user notifications and updates as well as sub-lists for each large area of research within the Rogues Gallery testbed infrastructure.

Please note that the MS Teams group for CRNCH Rogues Gallery may be the quickest way to post questions. However, the GT "SYMPA" mailing lists can also be used for discussion and will be used for subarea-specific announcements.

# 5.6 Mailing lists

To subscribe/unsubscribe from a mailing list please use this SYMPA FAQ page. Note that most lists are closed to external users.

- crnch-rg-users@lists.gatech.edu general user list. Mainly used for announcements and very high-level discussion.

- $\bullet \ \ crnch-rg-fpga@lists.gatech.edu \ \ Discussion \ of \ FPGA \ and \ reconfigurable \ computing$

- crnch-rg-nearmem@lists.gatech.edu Discussion of the Emu system and near-memory computing hardware like HBM, HMC, and NVDIMM

- crnch-rg-networking@lists.gatech.edu Discussion of in-network computing, FPGA networking, and edge computing/5G

- $\bullet \ crnch-rg-neuro-sysml@lists.gatech.edu-Discussion of neuromorphic computing and systems for machine learning \\$

- crnch-rg-quantum@lists.gatech.edu Discussion of quantum computing

# **5.7 Vendor Forums**

If we can't answer your question via chat, we may direct you to the relevant vendor forum for more assistance. See a list of related vendors here.

5.7. Vendor Forums

| tion, Release 1.0 |  |  |

|-------------------|--|--|

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

|                   |  |  |

#### **VENDOR FORUMS**

In many cases, we hope that the Rogues Gallery Teams group can be helpful to solving basic issues with novel hardware. However, at some point it is likely that you will need to post on a vendor-related forum. We have collected links to specific forums here and encourage you to sign up for the architecture you are working on.

#### 6.1 Intel FPGA

- Intel's main forum can be found here. Note that the https://community.intel.com/ site replaces Altera's old forum.

- Intel vLab clusters or Intel HARP has a ReadTheDocs and you can email them at iam@intel-research.net for questions specific to the cluster environment. HARP specifically has a private user forum here.

- OPAE has some support resources listed on their Github for the OPAE SDK, but the mailing list seems inactive.

- Intel's general support resources site can be found here.

#### 6.2 OneAPI

• Intel has a community forum for OneAPI and also a Discord that they use for workshops and tutorials.

#### 6.3 Xilinx FPGA

- · Xilinx forums

- Community portal Includes link to forums and open-source designs

#### 6.4 RISC-V Forums

- Chipyard Google Group for Chipyard-specific issues

- RISC-V Hardware Development Google Group

- Chisel Google Groups for questions specific to Chisel usage and debugging

- Chisel Gitter

- Chisel Community Resources

# 6.5 Lucata Corporation

- Check out the CRNCH RG Slack!

- Lucata has a private issue tracker on Github, if you have bugs to report. Please ask about this in the Teams channel, and we will help you post your issue.

# **6.6 Neuromorphic Computing**

• Nengo forum

# 6.7 Mellanox Networking

• Community forum

#### 6.8 Arm

- Community forum

- Arm HPC User Group Slack

#### CONTRIBUTING TO THIS DOCUMENTATION

We welcome and appreciate your comments and contributions to this documentation. Often, we rely on a mix of vendor support and community support for novel architectures and in many cases *you* are the expert just by starting to work with this new, novel architecture or software stack. This page presents some suggestions for contributing your own documentation.

# 7.1 What is the process for contributing documentation?

To contribute documentation, you should write an rst-formatted file related to your topic and submit it via pull request to this repository. We will also eventually have a form where you can upload and submit new documentation to be posted in a simplified fashion.

All read-the-docs documentation uses Restructered Text, so we ask that you write documentation in this format or convert Markdown files for your pull requests. However, we can also accept updates in Markdown format and integrate them into this repo.

#### 7.1.1 Current Topic Areas:

- Emu/Lucata

- Getting Started general topics needed to get started with RG

- Miscellaneous

- Networking in-network computing, 5G, and edge.

- · Neuromorphic and Novel Systems for ML

- Reconfig all FPGA-related documentation

- Quantum

- · Related all related work

#### 7.1.2 How do I update existing documentation?

- 1) Fork this repo.

- 2) Find the page you are looking to update and make your edits.

- 3) Add the page to the index file.

- 4) Build the code to test your code locally (requires Python and sphinx).

- 5) Commit and push to your fork and initiate a pull request.

#### 7.1.3 How do I contribute new documentation?

- 1) Fork this repo.

- 2) Find the folder you are looking to update and create a new page with the following titleformat: [Topic Area]-my-new-documentation-page.

- \* As an example, creating a new page for reconfigurable resources might have a title like: [Reconfig]-Using-Vitis-for-AI.rst

- \* Note that you may need to create your page with the appropriate .rst suffix name and then edit it to get appropriate formatting in the browser. You can check basic format of commits in the Github web interface.

- 3) Commit and push to your fork and initiate a pull request.

# 7.2 What should my documentation contain?

- 1) A useful title

- \* Ex: "Compiling ROS for the AC701 FPGA platform"

- 2) A brief description of the problem you're trying to solve.

- \* Ex: "This documentation details how to compile ROS for AC701 using the flubber server".

- 3) Code snippets that demonstrate proper execution of a technique or application for the topic in question. See the suggested format for code snippets below.

- 4) References to relative links from official documentaiton or examples, if they are relevant.

#### 7.3 Where should I add new files?

Ideally, your file should go under a directory related to your given topic. Please name your file with hyphens if it is a long filename, e.g., *reconfig-new-quartus-tools.rst* and place it under the correct folder in your commit. If you're not totally sure where a file should go, feel free to submit a pull request and we can help you format and find the right place for your file.

#### 7.4 How to convert MarkDown files to RST

Note that we prefer RST formatted documentation since that is used natively by ReadTheDocs. However, if you can only submit Markdown documentation this is also very helpful and appreciated!

While there are many nice GUI-based editors for MarkDown files, there are not that many editors for Restructered Text. One approach to contributing documentation would be to write it in Markdown and then convert it with Pandoc. This URL shows a simple example that we have repeated below.

```

pandoc rg-overview.md --from markdown --to rst -s -o rg-overview.rst

#You can also use the shortened version of this command and pandoc will infer the right

→syntax

pandoc -s rg-overview.md -o rg-overview.rst

```

You can use this simple script to convert a MarkDown file to RST, but you may then want to check that the links and figure links get populated correctly. You can also use editors like Typora to edit Markdown and then export an RST file. Note that Typora uses pandoc behind the scenes to do this conversion!

You can also use Python tools like m2r which may provide a better translation capability than pandoc.

# 7.5 Style Guide Suggestions

#### 7.5.1 How do I add a figure?

- 1) Add your figure to the docs/figures directory with a reasonable title. As an example, the overview page uses the figure RG\_CCRI\_Infrastructure\_Overview.png.

- 2) Use RST syntax to add it the appropriate page.

```

#Adds the image with a relative path to the figure directory.

#Alt tag is nice to have if the image does not load correctly

.. figure:: ../figures/general/RG_CCRI_Infrastructure_Overview.png

:alt: RG CCRI Infrastructure Overview

```

3) Commit your change and check the hosting page to see if it looks reasonable (placement, height, width, etc.). Proceed with the pull request as normal.

#### 7.5.2 How do I add code snippets?

You can use either two `` to delineate small segments of RST code or the ".. code::" tag to add indented code blocks. Check the figure instructions above for an example!

#### 7.6 Questions?

Please email us via our ticketing system crnch-help@cc.gatech.edu with any questions or please feel free to ask on our CRNCH Rogues Gallery MS Teams group.

# 7.6.1 What are all these errors from Sphinx about "Title underline too short"

Errors like *Title underline too short*. mean that the header underline needs to be the same length as the text. This is a strict requirement for Sphinx, which usually results in a warning.

#### **TESTBED RELEASE NOTES**

This page provides a high-level update on hardware and software that has been added or updated.

### **8.1 September 2023**

#### 8.1.1 Hardware Updates

• Rudi2, an AGX Orin Devkit, has been added to the testbed

# 8.2 August 2023

#### 8.2.1 Software Updates

• Open OnDemand 3.0.1 installed and deployed (upgrading from 2.0.32)

#### 8.2.2 Hardware Updates

#### 8.2.3 Documentation Updates

• VS Code instructions updated along with instructions for SSH jump host usage

# 8.3 July 2023

#### 8.3.1 Software Updates

- OneAPI 2023.1 Base and HPC Toolkits have been installed system-wide.

- New modulefiles added for Quartus FPGA tools available on relevant nodes.

- New VM for CI workflows has been added to the testbed.

- ROCm 5.6 installed on instinct.

- Lucata Pathfinder Toolkit 27.03 has been installed for relevant nodes.

- Xilinx Vitis, Vivado, and Vivado HLS 2022.2 and 2023.1 toolchains installed and updated.

### 8.3.2 Hardware Updates

- Violet nodes have been added as a new research resource with Sapphire Rapids CPUs.

- Bittware 840F Agilex FPGA card has been installed in flubber8.

#### 8.3.3 Documentation Updates

- VTune profiling page added

- Container migration to PACE page added

### 8.4 June 2023

### 8.4.1 Software Updates

• NVHPC 2023.5 SDK installed on all NVIDIA GPU nodes.

**CHAPTER**

**NINE**

# **RG DOCUMENTATION AUTHORS**

### 9.1 Current maintainers:

• Jeff Young

# 9.2 Community Contributors (listed alphabetically):

- Yujen Juan, Lucata Corporation

- Simrat Kaur, Illinois Tech

- Jason Riedy, Lucata Corporation

- Ron Rahaman, Georgia Tech

- James Wood, Georgia Tech

| Crnch Rogues Gallery Documentation, Release 1.0 |  |

|-------------------------------------------------|--|

| ,                                               |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

|                                                 |  |

**CHAPTER**

**TEN**

#### **USING SLURM WITH RG SYSTEMS**

See this page with examples of how to use Slurm to request jobs on the testbed!

# 10.1 What is Job Scheduling and Why Do We Use It?

Job scheduling helps us to manage a limited number of novel resources with an active userbase while guaranteeing the resources you need to finish your job. While job scheduling is currently most used for homogeneous cluster resources like PACE's Phoenix cluster we have focused on using it for the Rogues Gallery to provide fair access to all users and to help document how specific resources are utilized.

We use Slurm as our job scheduler and resource manager as it is widely used by large cluster installations including Cori and Perlmutter at NERSC, Frontera at TACC, and near-term systems like Frontier at ORNL. Since the Rogues Gallery has a large diversity of resources, we have many different *workflows* depending on the novel architecture that is targeted.

# 10.2 What Slurm queues are available?

You can check the current status of all queues by using sinfo --federation on any RG node. The Pathfinder runs as a "federated" Slurm cluster since it has a different host environment than the other RG nodes.

#### 10.3 Slurm Partitions

| Queue<br>Partition    | Time<br>Limit | Node | Node List                               | Notes                                                                      |

|-----------------------|---------------|------|-----------------------------------------|----------------------------------------------------------------------------|

| rg-<br>pathfinder     | No<br>limit   | 32   | c0n[0-7],c1n[0-<br>7],c2n[0-7],c3n[0-7] | Lucata Pathfinder system                                                   |

| rg-arm-<br>debug      | 4 hours       | 4    | octavius[1-4]                           | Used to compile/profile code                                               |

| rg-arm-<br>long       | 12<br>hours   | 16   | octavius[1-16]                          | Used for longer running jobs                                               |

| rg-gpu                | 12<br>hours   | 7    | frozone[1-<br>4],instinct,quorra[1-2]   | Different types of GPU-focused nodes for classes and neuromorphic research |

| rg-hpc                | 12<br>hours   | 3    | flubber[8-10]                           | General HPC nodes                                                          |

| rg-intel-<br>fpga-hw  | 12<br>hours   | 2    | flubber[2-3]                            | Hosts Intel FPGAs                                                          |

| rg-xilinx-<br>fpga-hw | 12<br>hours   | 2    | flubber[1-3]                            | Hosts Xilinx FPGAs                                                         |

| rg-smart-<br>nic      | 12<br>hours   | 2    | flubber[6-7]                            | SmartNIC nodes                                                             |

| notebook              | 12<br>hours   | 1    | hawksbill                               | Used to run Jupyter notebooks for tutorials, data analysis                 |

# 10.4 How do I get started with Slurm on RG?

We suggest that you first check out the following Slurm "Getting Started" resources from LLNL if you have not used a batch submission system before.

Then please check out our RG Slurm Examples page and the RG Workflows page for architecture of interest and specific commands to run for these systems.

- RG Slurm Examples

- · RG Workflows

#### **10.4.1 Important Slurm Commands**

Please consider looking at PACE's training information for Slurm as well.

- sinfo See status of queues and what is active/idle.

- squeue See the status of your jobs. You can also run squeue -u <username> to just list your jobs.

- scancel Used with the JOBID reported by squeue to cancel a job.

Options to run jobs include the following commands: - salloc - request resources from the Slurm scheduler and run a task when resources are ready - sbatch - create a batch file for later execution of one or more programs - srun - run parallel tasks across multiple processes. Called after salloc/sbatch.

#### **Slurm General Resources**

- Slurm Quickstart User Guide

- LLNL Slurm User Manual

- LLNL Slurm QuickStart Guide

- LLNL Slurm Commands Reference

- University of Maryland Torque versus Moab Guide Reference

- Princeton Research Computing's Slurm learning resources

- Slurm Video Tutorials

**CHAPTER**

#### **ELEVEN**

#### **OPEN ONDEMAND**

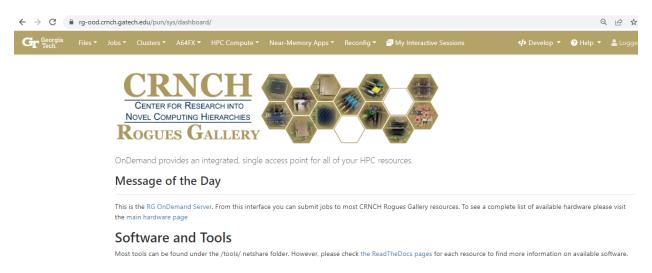

With the arrival of Slurm scheduling for most resources, we have switched to using Open OnDemand (sometimes called OOD) for GUI and notebook interfaces. Open On Demand provides a web browser interface from which users can launch GUI-based applications including Jupyter notebooks, file browsers, command-line terminals, and VNC-based applications. We encourage you to review the general PACE instructions for more details on what you can do with OOD - this page covers RG-specific tasks that you might find useful.

**Note:** OOD depends on using Slurm to reserve parts of nodes. This means that you will need to predict how long your job will take and how many cores your job needs. A compile that may take 3-4 hours should be run with a job that lasts at least that long.

## 11.1 Logging In

You should be able to log into the CRNCH RG Open OnDemand portal using your GT login and password with rg-ood.crnch.gatech.edu. If you are a GT employee or student, you will also need to use two-factor authentication (i.e., Duo) with your login while guests are not required to use two-factor login. Once you log in, you will be greeted by the login portal which has several tabs at the top of the webpage.

## 11.2 VNC for GUI applications

We have switched to using VNC instead of other tools like x2go because it is easier to schedule and works better with Open OnDemand.

**Note:** Like with x2go, your VNC session runs with a VNC server and will remain running for the length of your scheduled job, even if you need to close your laptop or the session tab. You can go to My Interactive Sessions to resume any running job.

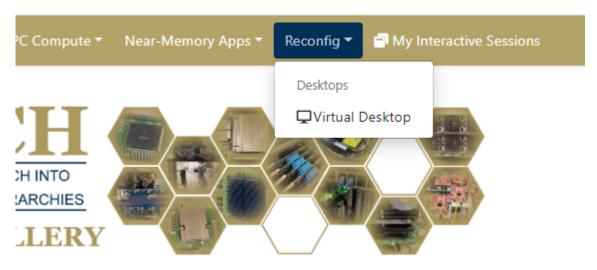

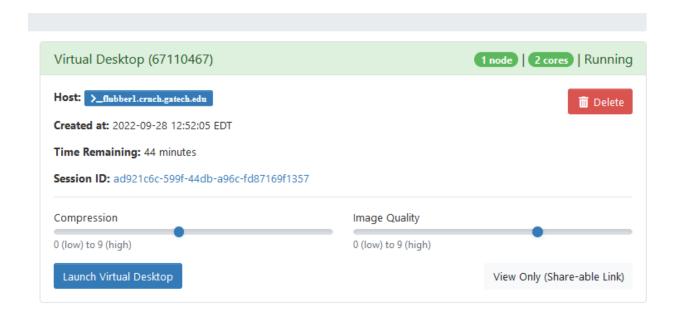

To run a job on one of the reconfigurable server nodes, please select Reconfig-->Virtual Desktop.

On the next page, you will need to specify the length of your job (we suggest 1-2 hours for non-compilation jobs), the number of cores to use (2-4 unless doing a parallel compile), and the queue (rg-xilinx-fpga-hw for flubber1 or rg-intel-fpga-hw for flubber2).

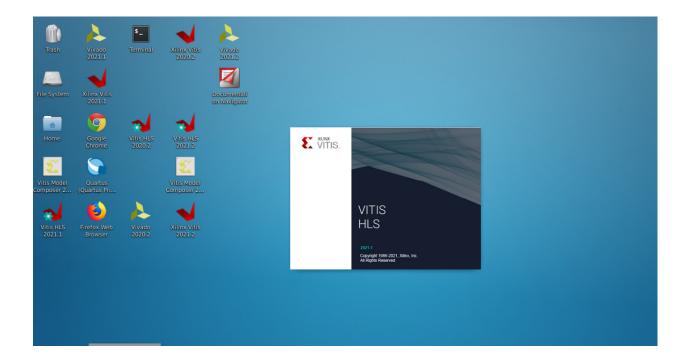

Once the job starts, you can change the image quality and compression settings for the VNC session to make your connection faster. Note that higher graphical quality may result in some lag on slower network connections. Click on Launch Virtual Desktop to start your VNC session.

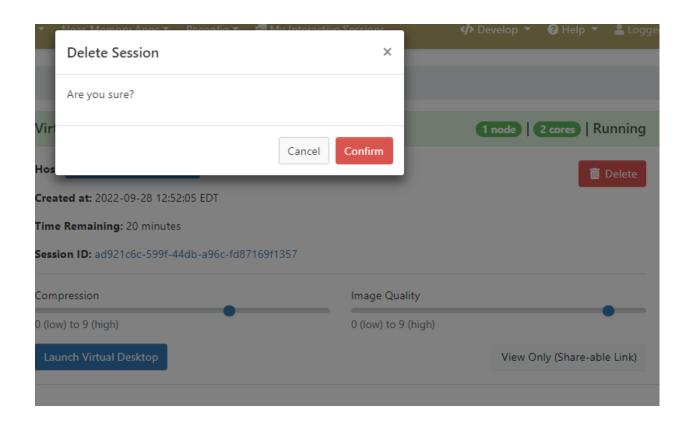

When you are completely finished with your VNC job, you can go back to your Interactive Sessions tab and select "Delete" to kill the VNC server and your job.

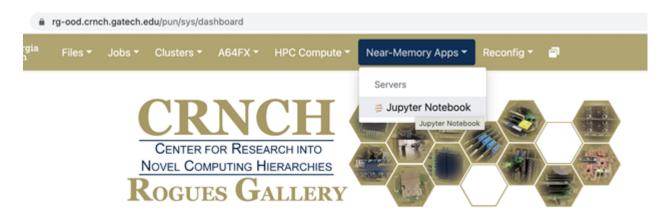

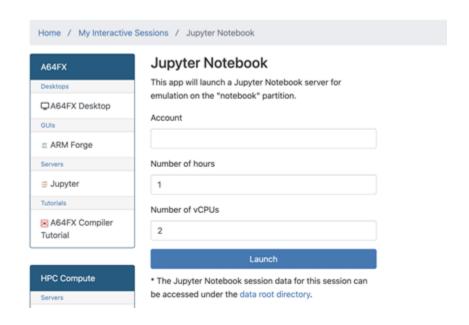

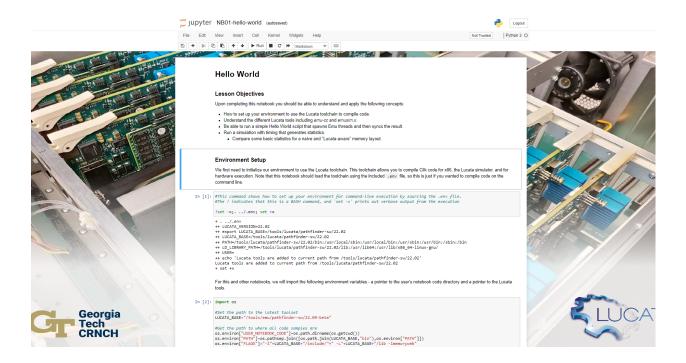

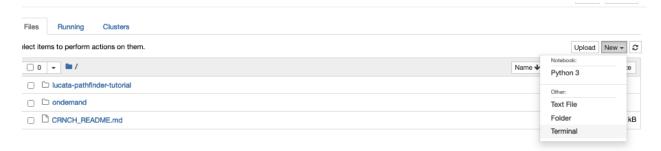

## 11.3 Jupyter Notebooks

To use Jupyter notebooks on our notebook server, hawksbill, you can select Near-memory Apps-->Jupyter Notebook.

You will then need to specify the time for your job (up to 12 hours) and the number of cores. We typically recommend starting with 2 cores unless you know you are running a parallel application from within your notebook.

Once the job launches, you can select Connect to Jupyter to connect to the Jupyter notebook interface.

You can then work within a Jupyter notebook to complete your project or experiments. Remember to save your notebook when you are finished and "Halt" when switching to other notebooks to save CPU resources.

## Virtual Desktop

This app will launch an interactive desktop on one or more Flubber compute nodes. You will have full access to the resources these nodes provide. This is analogous to an interactive batch job.

| Account                                                            |  |  |  |

|--------------------------------------------------------------------|--|--|--|

|                                                                    |  |  |  |

| Number of hours                                                    |  |  |  |

| 1                                                                  |  |  |  |

| Number of nodes                                                    |  |  |  |

| 1                                                                  |  |  |  |

| Queue                                                              |  |  |  |

| rg-xilinx-fpga-hw                                                  |  |  |  |

| $\square$ I would like to receive an email when the session starts |  |  |  |

| Launch                                                             |  |  |  |

|                                                                    |  |  |  |

<sup>\*</sup> The Virtual Desktop session data for this session can be accessed under the data root directory.

Fig. 1: You can then run applications from the terminal within the XFCE window or by using desktop icon launchers to launch GUI applications.

OnDemand provides an integrated, single access point for all of your HPC resources.

| □ 0                        |

|----------------------------|

| □                          |

| ☐ helpers                  |

| □ ■ NB01-hello-world.ipynb |

| ☐ ■ NB01.1-Plotting.ipynb  |

| ☐ hello-world-naive.c      |

| ☐ hello-world-spawn-at.c   |

| ☐ hello-world-spawn.c      |

| ☐ hello-world.c            |

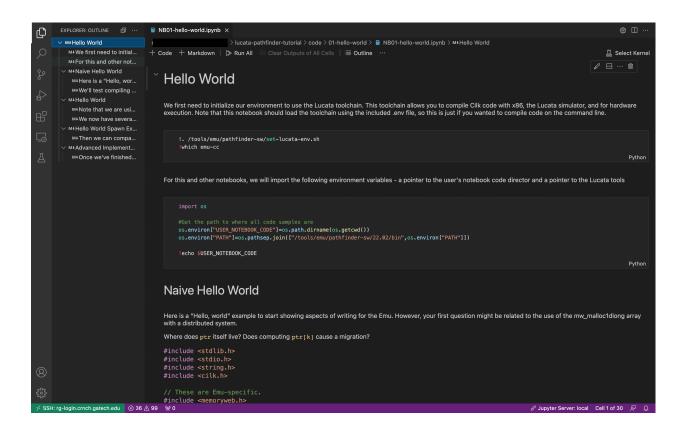

You can also open a terminal from the Jupyter notebook environment, which is useful if you are mixing C or other code in your notebook. The Lucata Pathfinder Tutorial has several examples of C-based code that can be run from the notebook or on the command line.

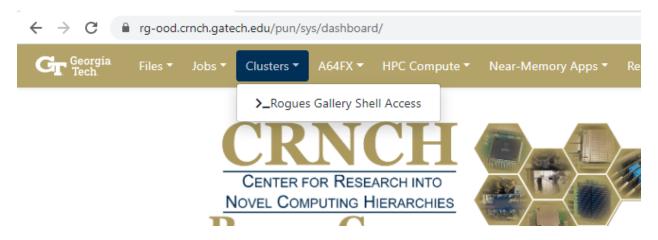

#### 11.4 Terminal from the Browser

To open a terminal on the main gateway node, rg-login.crnch.gatech.edu, you can select Clusters-->Rogues Gallery Shell Access.

```

🗂 jupyter

```

```

crunch30@hawksbill:-$ /netscratch/tutorials/hpec-tutorial-2022/

lucata-pathfinder-tutorial/ update_pf_tut_repo.sh

crunch30@hawksbill:-$ /netscratch/tutorials/hpec-tutorial-2022/update_pf_tut_repo.sh

Updating a local copy of the Pathfinder tutorial repo

crunch30@hawksbill:-$

```

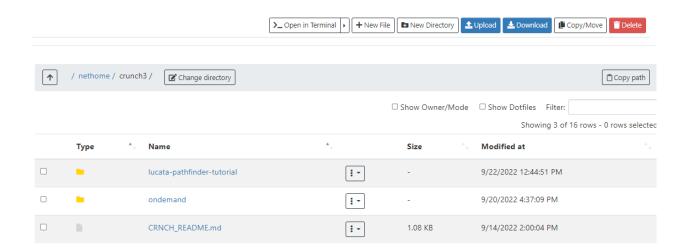

#### 11.5 File Browser

Open OnDemand includes a file browser, that you can use to open and investigate certain files in your netshare folder and your netscratch folder.

## 11.6 Troubleshooting

- 1) When launching a new job, the job may fail to launch with an I/O error.

- Failed to submit session with the following error: sbatch: error: Batch job submission failed: I/O error writing script/environment to file

- Try to relaunch the job. This may just be related to small OOD bugs.

- 2) When opening a VNC or Virtual Desktop session, you get the error "Failed to establish a websocket connection".

- Clear the cache in your web browser, relogin and try to launch the job again. Specifically you may need to clear your cookies for gatech.edu domains.

- 3) If you are having trouble copying and pasting text from your local machine to the VNC window, please try opening the VNC session using Chrome. Firefox security policies seems to limit copy-paste to webpages using JavaScript.

#### 11.6.1 More Resources

- Using OOD for the Lucata Pathfinder tutorial

- PACE OOD Guide PACE's Open OnDemand instructions

- Open OnDemand Discourse community discussions and a good place for Q&A

**CHAPTER**

**TWELVE**

#### **VISUAL STUDIO CODE**

**Note:** For remote GUI applications, we currently recommend using Open OnDemand.

You are welcome to use Visual Studio Code (VS Code or VSC) along with the Remote Development Extension Pack to SSH to Rogues Gallery resources. This allows you to navigate folders and edit code with the power and convenience of VS Code and its many excellent extensions.

**Warning:** We highly recommend that you add a jump host to *hawksbill* and run VS Code from that node rather than on the login node, *rg-login*. Please see this page about setting up SSH jump hosts for this purpose.

Recommended Extensions Include:

- Remote Development Includes the Remote SSH, Remote Container, and Remote WSL extensions

- · Remote SSH required to interact with remote SSH sessions on RG

- Jupyter can be used to interact with and execute Jupyter notebooks from VSC.

Optional Extensions May Include:

- C/C++ C syntax highlighting

- Python Python highlighting

## 12.1 VSC and SSH Config Files

If you use VS Code, it is recommended to set up an SSH configuration file for easy access to RG nodes. In this way, you don't have to remember hostnames or worry about whether you are on the campus VPN or not.

- After installing the Remote Development Extension Pack, click the green button on the bottom left corner of the screen.

- 2. A dialog will open at the top, select Connect to Host then select Configure SSH Hosts....

- 3. You should have at least one config file listed here, if there are multiple then just select the one associated with your current user.

- 4. This will open the config file in the VS code editor, from here follow this format to add a host to your file:

Host rg-Login

HostName rg-login.crnch.gatech.edu

User gburdell

```

Host rg-Neuro-Dev

HostName rg-neuro-dev.crnch.gatech.edu

User gburdell

ProxyJump rg-Login

```

```

≡ config

X

> .ssh > ≡ config

Users >

Host rg-Login

HostName rg-login.crnch.gatech.edu

3

User gburdell

IdentityFile ~/.ssh/id_rsa

Host rg-Neuro-Dev

HostName rg-neuro-dev.crnch.gatech.edu

User gburdell

IdentityFile ~/.ssh/id_rsa

10

ProxyJump rg-Login

11

```

This has added rg-login, and below that rg-neuro-dev. Pay special notice to the ProxyJump option which will route your connection to rg-neuro-dev through rg-login first.

Now, if you select that green button again, then Connect to Host, you can pick either rg-login or rg-neuro-dev as options.

## 12.2 VSC with Jupyter Notebooks

Special Thanks to our Contributing Authors for this Page: James Wood

| Crnch Rogues Gallery Documentation, Release 1.0 |  |  |  |  |

|-------------------------------------------------|--|--|--|--|

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

|                                                 |  |  |  |  |

**CHAPTER**

### **THIRTEEN**

#### PYTHON ENVIRONMENTS

**Note:** TLDR: we recommend that you use pipenv on CRNCH environments rather other Python package managers or tools like conda/anaconda. See the pipenv section for more details on usage.

## 13.1 FAQs on CRNCH Python Environments

- The default Python is typically 3.8. We do not officially support Python 2 usage as most packages have updated to support Python 3.

- Look into 2to3 if your code is still using Python 2!

- virtualenv and venv is installed across most of our servers and as many dev boards as possible.

- We recommend to use either virtualenv or venv with pip or pipenv to install packages into your local virtual environments. Note that venv and pip are default packages for all Python 3.3+ installations, and venv contains a subset of virtualenv functionality.

- We do not typically recommend using conda, miniconda, or anaconda as these quickly eat up home directory space.

- However, if you want to use conda or miniconda please consider using miniconda with your scratch space folder to store your conda environment and venvs. See the example below under the Conda section as a template.

## 13.2 What's the difference between pip, venv, env, conda, etc?

Supported Purpose Tool Default on Notes Name Python Ver-**CRNCH** sions RG pip All Versions Default package manpipenv 2+ Y Combines pip and virtualenv Package, dependency, and environment manvir-2+Environment manager tualen venv 3.3 +Y venv is a subset of virtualenv installed by default Environment manager with Python 3.3+ NA Suggested version of conda to use on RG; Installs mini-Minimalist package N conda environment its own conda/Python as well as non-Python manager Package and environana-NA Not supported on RG; Installs its own Python conda ment manager po-3.7 +Package and depen-N Not supported on RG

**Table 1: Python Environment Tools**

## 13.3 Using venv on CRNCH RG

Venv is the default virtual environment module included since Python 3.3, and it totally replaces *pyenv* since Python 3.6. Virtualenv has many similarities to venv in terms of its functionality, but we recommend using venv unless you need to use a version of Python older than 3.3.

#### 13.3.1 Creating a new virtual environment with venv

dency manager

```

$ mkdir myproject

$ python -m venv myproject

# OR to create a specific Python version venv use the following command instead

$ mkdir my311project

$ python3.11 -m venv my311project

```

#### 13.3.2 Activating/deactivating an environment

```

$> source myproject/bin/activate

//To leave type exit

(myproject)gburdell@rg-login:$ exit

//For our 3.11 version venv above

$> source my311project/bin/activate

(my311project) gburdell@rg-login:~$ python -V

Python 3.11.2

```

etry

#### 13.3.3 Installing and using packages

Here we demonstrate a basic usage of pip with venv. We highly recommend using pipenv, which provides a more robust combination of pip and virtual environments.

```

$ source myproject/bin/activate

(myproject)gburdell@rg-login:$ pip install matplotlib

Collecting matplotlib

Downloading matplotlib-3.6.2-cp38-cp38-manylinux_2_12_x86_64.manylinux2010_x86_64.whl (9.

\hookrightarrow4 MB)

9.4/9.4 MB 56.5 MB/s eta 0:00:00

//Use pip freeze to generate a requirements.txt file which can be used to reinstall a.

⇒specific environment in the future.

pip freeze > requirements.txt

(myproject) gburdell@rg-login:~/USERSCRATCH/myproject$ ls

bin include lib lib64 pyvenv.cfg requirements.txt share

(myproject) gburdell@rg-login:~/USERSCRATCH/myproject$ more requirements.txt

contourpy==1.0.6

matplotlib==3.6.2

numpy = 1.24.1

six = 1.16.0

```

## 13.4 Using pipvenv on CRNCH RG

Pipenv combines the best parts of the pip package manager for Python and virtual environments, as typified by virtualenv and venv. One key difference is that pipenv keeps all of its dependencies for installations in a Pipfile that can then be used to regenerate a specific environment. Pipenv uses TOML syntax, and one Pipfile can be used in place of multiple requirements.txt files created by Pip with virtual environments. The Pipfile.lock file provides a secure hashed record of installations that can be used for future deployments.

#### 13.4.1 Installing pipenv

Using the official installation instructions here:

```

python3 -m pip install pipenv

```

#### 13.4.2 Creating a new virtual environment with pipenv

When you run pipenv install, it will create a standard virtual environnment and all related pip installs will occur within this user-accessible folder.

```

$ pipenv install

Creating a virtualenv for this project...

Pipfile: /nethome/gburdell/Pipfile

Using /usr/bin/python3.8 (3.8.13) to create virtualenv...

Creating virtual environment...created virtual environment CPython3.8.13.final.0-64.

```

(continues on next page)

(continued from previous page)

```

→in 2991ms

creator CPython3Posix(dest=/nethome/gburdell/.local/share/virtualenvs/gburdell-

→hxKrwMjp, clear=False, no_vcs_ignore=False, global=False)

seeder FromAppData(download=False, pip=bundle, setuptools=bundle, wheel=bundle,

yvia=copy, app_data_dir=/nethome/gburdell/.local/share/virtualenv)

added seed packages: pip==22.3, setuptools==65.5.0, wheel==0.37.1

activators BashActivator, CShellActivator, FishActivator, NushellActivator,

→PowerShellActivator, PythonActivator

√ Successfully created virtual environment!

Virtualenv location: /nethome/gburdell/.local/share/virtualenvs/gburdell-hxKrwMjp

Pipfile.lock not found, creating...

Locking [dev-packages] dependencies...

Locking [packages] dependencies...

Updated Pipfile.lock (db4242)!

Installing dependencies from Pipfile.lock (db4242)...

0/0 - 00:00:00

To activate this project's virtualenv, run pipenv shell.

Alternatively, run a command inside the virtualenv with pipenv run.

If you'd like to create a Python 3.8 environment, use the following syntax. Note that

→this will overwrite the standard location for your virtualenv

```

```

pipenv install pipenv --python 3.8 install

```

#### 13.4.3 Activating/deactivating an environment

```

$ pipenv shell

Launching subshell in virtual environment...

. /nethome/gburdell/.local/share/virtualenvs/gburdell-hxKrwMjp/bin/activate

gburdell@rg-login:~$ . /nethome/gburdell/.local/share/virtualenvs/gburdell-hxKrwMjp/bin/

activate

(gburdell) gburdell@rg-login:~$

```

OR use the code::pipenv run method

```

$ python3 --version

Python 3.6.8

$ pipenv run python3 --version

Python 3.8.13

```

#### 13.4.4 Installing and using packages

```

$ pipenv install 2to3

Installing 2to3...

Adding 2to3 to Pipfile's [packages]...

✓ Installation Succeeded

Pipfile.lock (db4242) out of date, updating to (7d7dfd)...

Locking [dev-packages] dependencies...

Locking [packages] dependencies...

Building requirements...

Resolving dependencies...

✓ Success!

Updated Pipfile.lock (7d7dfd)!

Installing dependencies from Pipfile.lock (7d7dfd)...

0/0 - 00:00:00

To activate this project's virtualenv, run pipenv shell.

Alternatively, run a command inside the virtualenv with pipenv run.

```

To show what packages are installed and their dependencies, you can use pipenv graph. Here we show the dependencies for 2to3 and matplotlib.

```

$ pipenv graph

//No dependencies for this package

2to3==1.0

//Several dependencies were installed, including numpy

matplotlib==3.6.2

- contourpy [required: >=1.0.1, installed: 1.0.6]

- numpy [required: >=1.16, installed: 1.24.1]

- cycler [required: >=0.10, installed: 0.11.0]

- fonttools [required: >=4.22.0, installed: 4.38.0]

- kiwisolver [required: >=1.0.1, installed: 1.4.4]

- numpy [required: >=1.19, installed: 1.24.1]

- packaging [required: >=20.0, installed: 23.0]

- pillow [required: >=6.2.0, installed: 9.4.0]

- pyparsing [required: >=2.2.1, installed: 3.0.9]

- python-dateutil [required: >=2.7, installed: 2.8.2]

- six [required: >=1.5, installed: 1.16.0]

```

## 13.5 Pipenv Related Documents

- · Pipenv and Virtualenv

- · Pipenv guide

- Pipenv vs virtualenv vs conda environment

## 13.6 Pip

Pip or the *package installer for python* is the default way to install packages from the Python Package Index, or PyPI. Depending on the version of Python used, you may need to call it using code::*pip install <packagename>* or code::*python -m pip install <packagename>*.

Note that best practices specify that you should install packages into a "user-local" directory (normally under ~/.local or your virtual environment folder). You can find this location for your version of Python using the following command.

```

$ python3 -m site --user-base

/nethome/gburdell/.local

```

Then you can install packages to your local directory as follows. Assuming a standard Python 3.8 install, the installed files can be found at code::.local/lib/python3.8/site-packages/.

```

$ pip install --user matplotlib

```

#### 13.6.1 Pip Related Documents

• Python Pip tutorial page.

#### 13.7 Conda

**Note:** We typically don't recommend using anaconda due to the amount of dependencies it pulls into your home directory. If you get to where you need anaconda for a project this is typically some software that should be installed in a project space or system-wide! Please consider submitting a help ticket especially if you need multiple packages that can't be satisfied with pipenv.

#### 13.7.1 Miniconda Installation and Usage Example

With the above caveat in mind, this example shows how to use your scratch space to install and use Miniconda. We recommend this approach since this saves space in your home directory and because full Conda environments do not typically need to be backed up. Note that you can always use conda env export --from-history>ENV.yml to back up an installed environment.

(continues on next page)

(continued from previous page)

```

//Add the location of miniconda to your path. You should add this to your .bashrc file

export PATH=$PATH:~/USERSCRATCH/conda/conda3_22.11.1/bin && export LD_LIBRARY_PATH=$LD_

→LIBRARY_PATH:~/USERSCRATCH/conda/conda3_22.11.1/lib

//Create a new conda environment on your scratch space.

conda create --prefix ~/USERSCRATCH/condaenv/

Collecting package metadata (current_repodata.json): done

Solving environment: done

## Package Plan ##

environment location: /nethome/gburdell/USERSCRATCH/condaenv

Preparing transaction: done

Verifying transaction: done

Executing transaction: done

# To activate this environment, use

#

$ conda activate /nethome/gburdell/USERSCRATCH/condaenv

# To deactivate an active environment, use

#

$ conda deactivate

```

#### 13.7.2 Conda Related Documents

- Understanding conda and pip

- Explaining the many flavors of conda

- OLCF's guide to using conda, which assumes a sitewide installation of conda.

- NERSC's guide on using python with anaconda

13.7. Conda 53

## 13.8 Poetry

Poetry is a tool for dependency management and packaging similar to pipenv (which combines pip and venv). While we don't currently support it, you may be interested to try it out in your user-local setup. Read more about Poetry at the official website.

## 13.9 Bonus: IPython, IPykernel, and Jupyter

You may see some reference to IPython kernels which switching between virtual environments or especially for Jupyter notebooks. In short, IPython (see site) is a command shell for interactive Python execution that can be extended for GUI applications and parallel computing. Jupyter is a web-based interactive tool that builds on IPython but also supports many other kernels for languages like Julia and R. You can read more about kernels for Jupyter at this link.

**CHAPTER**

#### **FOURTEEN**

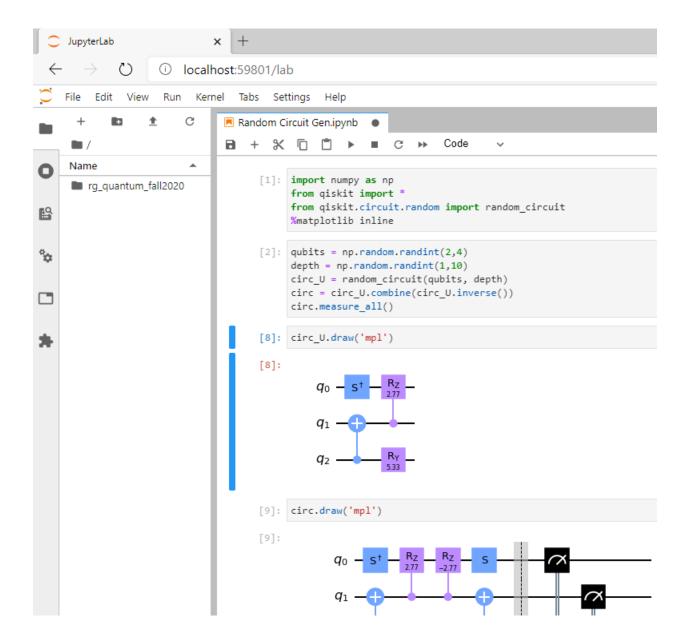

#### JUPYTER NOTEBOOKS

We suggest using JupyterLab as your interface for neuromorphic, quantum, and reconfigurable research. PACE has a nice article on using Jupyter notebooks we also recommend. Eventually we will support schedulable Jupyter notebooks via our Slurm scheduler.

*Note*: If you are running a long-running job like ML training we recommend that you don't use port forwarding as closing your local machine/web browser will likely stop or pause any actions within the Jupyter notebook. You alternatively can use VNC or x2go to create a remote server and you can then run your notebook within a browser in that remote terminal session.

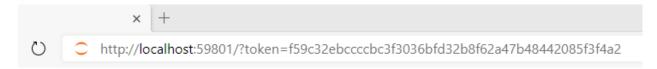

## 14.1 Using jump hosts to access Jupyter notebooks

Note that these techniques will let you use "port forwarding" to forward the Jupyter notebook to your local machine.

First connect from your local terminal to this server using SSH forwarding for a specific port:

```

ssh -L 59801:localhost:59801 -C -J rg-login.crnch.gatech.edu rg-quantum-dev.crnch.gatech.

⊶edu

```

Then start your JupyterLab instance on the node you want to use a notebook with:

```

rg-quantum-dev: $ jupyter-lab --no-browser --port 59801

[W 21:20:20.924 LabApp] JupyterLab server extension not enabled, manually loading...

[I 21:20:20.931 LabApp] JupyterLab extension loaded from /nethome/gtburdell/.local/lib/

→python3.8/site-packages/jupyterlab

[I 21:20:20.931 LabApp] JupyterLab application directory is /nethome/gtburdell/.local/

→share/jupyter/lab

[I 21:20:20.934 LabApp] Serving notebooks from local directory: /nethome/gtburdell/git_

→repos/vip_class

[I 21:20:20.935 LabApp] Jupyter Notebook 6.1.5 is running at:

[I 21:20:20.935 LabApp] http://localhost:59801/?

→token=f59c32ebccccbc3f3036bfd32b8f62a47b48442085f3f4a2

[I 21:20:20.935 LabApp] or http://127.0.0.1:59801/?

→token=f59c32ebccccbc3f3036bfd32b8f62a47b48442085f3f4a2

[I 21:20:20.935 LabApp] Use Control-C to stop this server and shut down all kernels.

→(twice to skip confirmation).

[C 21:20:21.002 LabApp]

To access the notebook, open this file in a browser:

file:///nethome/gtburdell/.local/share/jupyter/runtime/nbserver-14090-open.html

Or copy and paste one of these URLs:

```

(continues on next page)

(continued from previous page)

```

http://localhost:59801/?token=f59c32ebccccbc3f3036bfd32b8f62a47b48442085f3f4a2 or http://127.0.0.1:59801/?token=f59c32ebccccbc3f3036bfd32b8f62a47b48442085f3f4a2

```

Connect locally to the notebook using your web browser with the token provided.

```

http://localhost:59801/?token=f59c32ebccccbc3f3036bfd32b8f62a47b48442085f3f4a2

```

Note: Remember to close both your jump session and your jupyterlab session when you are finished!

## 14.2 Alternative method: use the provided setup script

This method provides a randomized port number for you to use and is preferred. It still requires creating a tunnel to your home machine but shares the string to do so with you:

```

./tools/misc/scripts/start_jupyter_notebook.sh

Connect to this instance using port forwarding in another terminal from your machine.

→with the following string: